【高速PCB设计】揭秘高速PCB设计中如何抑制并改善信号串扰问题

在当今飞速发展的电子设计领域, 高速化和小型化已经成为设计的必然趋势。与此同时,信号频率的提高、电路板的尺寸变小、布线密度加大、板层数增多而导致的层间厚度减小等因素,则会引起各种信号完整性问题。因此,在进行高速板级设计的时候就必须考虑到信号完整性问题,掌握信号完整性理论,进而指导和验证高速 PCB 的设计。

在所有的信号完整性问题中, 串扰现象是非常普遍的。串扰可能出现在芯片内部,也可能出现在电路板、连接器、芯片封装以及线缆上。深圳市桂科微电子公司工程师在设计中总结、整理、分析,将剖析在高速PCB板设计中信号串扰的产生原因,以及抑制和改善的方法。

串扰的产生

串扰是指信号在传输通道上传输时,因电磁耦合而对相邻传输线产生的影响。过大的串扰可能引起电路的误触发,导致系统无法正常工作。

串扰的分析

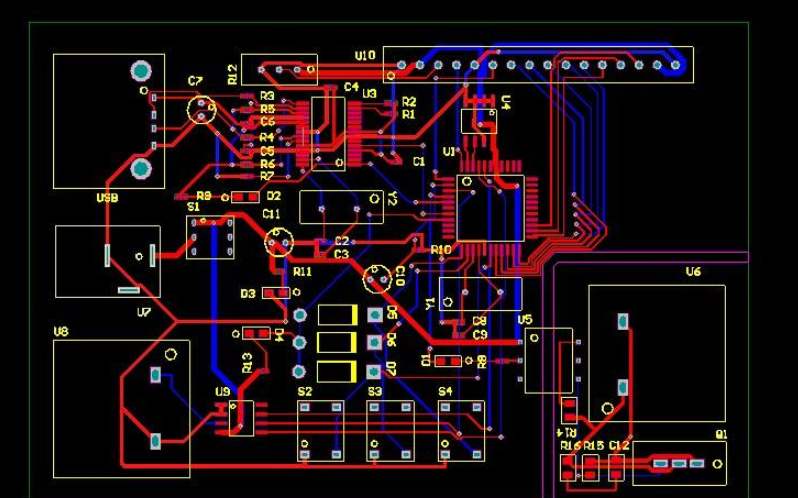

高速PCB设计的整个过程包括了电路设计、芯片选择、原理图设计、PCB布局布线等步骤,设计时需要在不同的步骤里发现串扰并采取办法来抑制它,以达到减小干扰的目的。

串扰的抑制

不管是设计前的串扰计算,还是布局布线前的仿真,或是布局布线后的仿真,都是为了使 PCB 板能快速达到最小的干扰。因此需要在设计过程中运用以前的经验来解决现在的问题,以下就是有效避免布局布线中串扰的经验总结:

1.容性耦合和感性耦合产生的串扰随受干扰线路负载阻抗的增大而增大,所以减小负载可以减小耦合干扰的影响;

2.尽量增大可能发生容性耦合导线之间的距离,更有效的做法是在导线间用地线隔离;

3.在相邻的信号线间插入一根地线也可以有效减小容性串扰,这根地线需要每1/4波长就接入地层。

4.感性耦合较难抑制,要尽量降低回路数量,减小回路面积,不要让信号回路共用同一段导线。

5.避免信号共用环路。在高速 PCB设计的过程中,不仅需要对理论概念的详细理解,同样需要不断的积累经验,不断完善理论。同时,对相关辅助软件的熟练运用也可以缩短设计周期,从而提高竞争力,对设计的成功完成起到重要的作用。

高速PCB板级、系统级设计是一个复杂的过程,包括信号串扰在内的信号完整性问题越来越不容忽视,因此需要设计者在设计的时候对信号完整性问题有全面的规划与考虑,在设计周期的各个阶段采用不同的方法来确保设计快速、精确地完成,从而节约时间、避免重复。

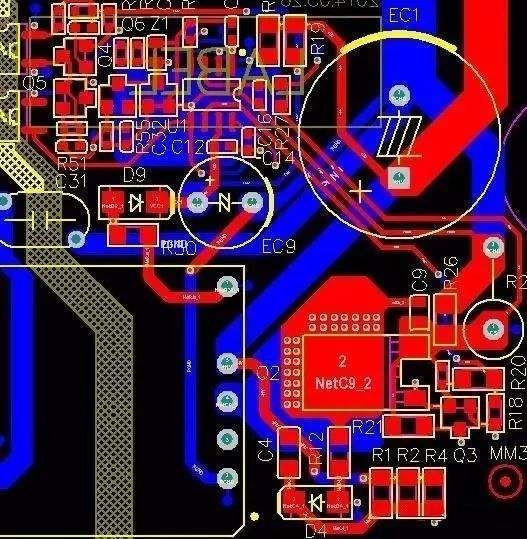

随着电路板上走线密度越来越高,信号串扰总是一个难以忽略的问题。因为不仅仅会影响电路的正常工作,还会增加电路板上的电磁干扰。

在电路板上的一些高频信号会串扰到电路或者MCU的I/O接口电路,形成共模电压,众所周知,共模电压在电路设计时是最让人讨厌的玩意儿,因此,设计电路板时要避免各种可能造成电路工作不正常的共模电压的串扰。

减小电路板上串扰的设计原则简单归类

1,通过合理布局使各个元器件之间的连线尽量短。

2,由于串扰程度和施加干扰信号的频率成正比,因此要使高频信号线远离敏感信号线。

3,施加干扰信号线与受到干扰信号线不仅要远离,最好要用地线隔离,并且避免相互平行走线。

4,在多层PCB板中,施加干扰信号线与受到干扰信号线或敏感信号走线要用地线隔离或相隔地层。

5,在多层PCB板中,施加干扰信号线与受到干扰信号线分别在地线或地层的相对两面,也就是隔层。

6,尽量使用输入阻抗较低的敏感电路,必要时可以使用旁路电容降低敏感电路的输入阻抗。